Sino a 12 core per i futuri processori AMD Opteron

AMD delinea quelle che saranno le principali caratteristiche tecniche delle proprie future cpu per sistemi server e workstation della famiglia Opteron. Passaggio prima a 6 core e successivamente a 12, ferma restando l'architettura di base che parte da quella Barcelona con una serie di innovazioni per incrementare le prestazioni per clock

di Paolo Corsini pubblicato il 08 Maggio 2008 nel canale Server e WorkstationAMD

Introduzione

Apriamo questo articolo tornando con la memoria al mese di Aprile 2003: in quel periodo AMD ha presentato la prima cpu basata sul proprio progetto noto con il nome in codice di Hammer, concretizzatasi nella forma dei processori Opteron per sistemi server seguita a Settembre dello stesso anno dalle prime soluzioni Athlon 64.

Con quella architettura, evolutasi nel corso degli anni prima con il passaggio a soluzioni dual core e in seguito con l'utilizzo di un memory controller compatibile con memorie DDR2, AMD ha conquistato una interessante quota di mercato nel ricco segmento delle soluzioni server, in particolare guadagnando una posizione di rilievo nei sistemi server con 4 o più Socket di processore per sistema. All'interno dei processori Opteron per la prima volta trovavano spazio tecnologie particolarmente efficienti in sistemi server, quali il memory controller integrato e una connessione come quella HyperTransport in grado di ridurre sensibilmente le latenze incrementando la bandwidth di intercomunicazione tra le periferiche.

Sino ad Aprile 2003 la presenza nel segmento server di AMD è stata pressoché nulla: ricordiamo alcuni timidi tentativi del produttore americano di guadagnare l'interesse dei produttori presenti con sistemi server con i processori Athlon MP, architetture per sistemi a due Socket interessanti quanto ad architettura ma non percepite, in quel momento, come soluzioni adatte a venir utilizzate in sistemi dei principali produttori OEM internazionali. L'impatto dei primi processori Opteron è stato quindi per certi versi rivoluzionario, in quanto ha permesso ad AMD di costruire una solida e stabile relazione con tutti i principali produttori mondiali di server.

Nel 2006 Intel ha presentato la propria architettura Core 2, offrendo differenti serie di processori prima dual core e in seguito anche quad core specificamente sviluppati per sistemi server a due Socket; il lancio di questa architettura ha generato una notevole competizione con AMD, non più in grado di poter vantare un vantaggio prestazionale netto su Intel non solo nel segmento desktop ma anche in quello delle soluzioni server. AMD è stata costretta a correre ai ripari presentando la propria evoluzione dell'architettura Opteron nella forma delle cpu quad core, note con il nome in codice di Barcelona.

Questi processori sono giunti sul mercato nel mese di Settembre 2007, in notevole ritardo rispetto a quanto inizialmente anticipato e con frequenze di clock ridotte rispetto a quelle delle soluzioni concorrenti di Intel. Non solo: un bug nella TLB della cache L3 dei processori Barcelona revision B2 ne ha di fatto bloccato la commercializzazione nel mondo dei sistemi server sino al mese di Marzo 2008, periodo nel quale sono stati immessi sul mercato i primi sistemi basati sulla revision B3 del processore Opteron quad core.

Gli ultimi 24 mesi sono stati indubbiamente molto difficili per AMD, non solo nel segmento delle soluzioni desktop ma anche in quello dei sistemi server: Intel è stata capace di riguadagnare quote di mercato in questa ricca nicchia di mercato. Più di questo, tuttavia, è venuta a mancare la fiducia dei partner AMD nella capacità del produttore americano di rispettare la propria roadmap dei prodotti alla luce dei ritardi e dei problemi che hanno caratterizzato il lancio delle cpu Opteron quad core.

Quest'oggi AMD ha scelto di rendere pubblica la propria futura roadmap dei processori per sistemi server, delineando sia quali saranno le novità architetturali implementate con tecnologia produttiva a 45 nanometri che la volontà di continuare a mantenere un approccio il più possibile di tipo nativo alle proprie architetture di processore per sistemi workstation e server.

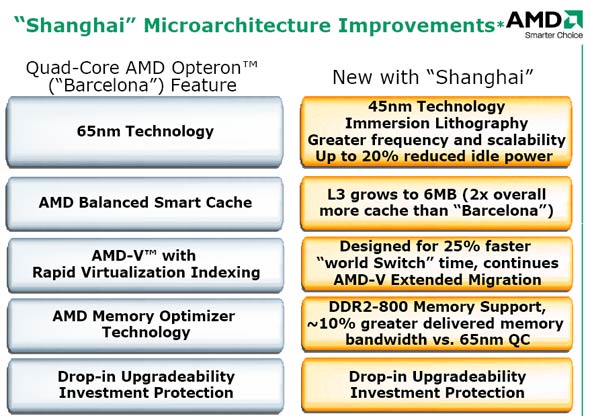

La prossima generazione di processori Opteron è indicata con il nome in codice di Shanghai; al pari delle soluzioni Barcelona attualmente disponibili in commercio troveremo 4 core di processore con design nativo, ma una superiore complessità architetturale grazie alle potenzialità della tecnologia produttiva più sofisticata data dal passaggio da 65 nanometri a 45 nanometri.

Come già evidenziato in differenti occasioni troveremo una cache L3 incrementata sino a 6 Mbytes rispetto agli attuali 2 Mbytes implementati nelle cpu Opteron Barcelona, fermo restando il quantitativo di cache L2 pari a 512 Kbytes per ciascuno dei core di processore. In termini architetturali AMD implementerà varie ottimizzazioni sia per incrementare l'IPC, instructions per clock, che per una più efficiente gestione della virtualizzazione, seguendo in questo il lavoro già fatto inizialmente con i processori Barcelona. Si prevede un incremento prestazionale medio del 20%, a parità di frequenza di clock, nel passaggio da Barcelona a Shanghai ma è bene attendere le opportune verifiche del caso non appena i primi sample di processore Shanghai saranno disponibili.

Troveremo novità anche nel memory controller, reso compatibile con memorie DDR2-800 contro quelle DDR2-667 delle cpu Opteron Barcelona: la conseguenza diretta, stante la piena maturazione della tecnologia DDR2, sarà la possibilità di incrementare la bandwidth massima teorica di ogni processore, sfruttando al meglio in questo l'integrazione del memory controller.

Le cpu Shanghai implementeranno link HyperTransport di tipo 3.0, contro quelli HyperTransport 1.0 adottati da AMD per i processori Barcelona; questo implicherà l'utilizzo di schede madri con Socket 1207+ per sfruttare al meglio la bandwidth addizionale dei link HT 3 ferma restando la compatibilità con le attuali piattaforme dotate di Socket a 1207 pin con link HT 1.

MSI Vector 16 HX A13V è un notebook gaming che fa sentire la sua potenza (e non solo)

MSI Vector 16 HX A13V è un notebook gaming che fa sentire la sua potenza (e non solo) In Photoshop arriva l'IA di nuova generazione

In Photoshop arriva l'IA di nuova generazione Navicella spaziale Boeing CST-100 Starliner: il lancio è rimandato al 25 maggio

Navicella spaziale Boeing CST-100 Starliner: il lancio è rimandato al 25 maggio Tutti gli Apple Watch in offerta: si parte da soli 199, ma ci sono diversi modelli molto interessanti

Tutti gli Apple Watch in offerta: si parte da soli 199, ma ci sono diversi modelli molto interessanti Edge 50 Pro 5G 12/256GB a 599 e altri affari Motorola da non perdere: G84 5G 12GB/256GB a 191 e G54 a 168

Edge 50 Pro 5G 12/256GB a 599 e altri affari Motorola da non perdere: G84 5G 12GB/256GB a 191 e G54 a 168 Ecco tutte le svendite Amazon del Weekend: super sconti Apple, portatili, tablet e smartphone ma anche molto altro!

Ecco tutte le svendite Amazon del Weekend: super sconti Apple, portatili, tablet e smartphone ma anche molto altro! Narwal Freo X Plus e Narwal Freo X Ultra sono oggi i migliori robot per rapporto prezzo prestazioni: torna il prezzo di lancio!

Narwal Freo X Plus e Narwal Freo X Ultra sono oggi i migliori robot per rapporto prezzo prestazioni: torna il prezzo di lancio! Tutti i MacBook in offerta su Amazon: si parte da 999, MacBook Pro -400 e anche gli Air 2002 e 2024 a prezzi bassi!

Tutti i MacBook in offerta su Amazon: si parte da 999, MacBook Pro -400 e anche gli Air 2002 e 2024 a prezzi bassi! La wallbox per la ricarica delle auto elettriche Osoeri è scesa a 360! Potenza fino a 22 kW, controllo via app e molto altro

La wallbox per la ricarica delle auto elettriche Osoeri è scesa a 360! Potenza fino a 22 kW, controllo via app e molto altro Google Pixel 8 Pro (825), iPhone 15 Pro Max 256GB: sono questi i top di gamma più scontati del weekend!

Google Pixel 8 Pro (825), iPhone 15 Pro Max 256GB: sono questi i top di gamma più scontati del weekend! Solo 269 il portatile low cost con 16GB/512GB e Win 11 e scende a 479 quello con AMD Ryzen 7 5700U 16GB/512GB!

Solo 269 il portatile low cost con 16GB/512GB e Win 11 e scende a 479 quello con AMD Ryzen 7 5700U 16GB/512GB! La NASA sarebbe ancora incerta sulla missione privata per salvare il telescopio spaziale Hubble

La NASA sarebbe ancora incerta sulla missione privata per salvare il telescopio spaziale Hubble Buchi neri in fase di fusione nell'Universo primordiale individuati dal telescopio spaziale James Webb

Buchi neri in fase di fusione nell'Universo primordiale individuati dal telescopio spaziale James Webb IBM lancia Qiskit 1.0: il software development kit per i computer quantistici arriva alla prima versione stabile

IBM lancia Qiskit 1.0: il software development kit per i computer quantistici arriva alla prima versione stabile Problema al sistema propulsivo per la sonda della missione ESA-JAXA BepiColombo

Problema al sistema propulsivo per la sonda della missione ESA-JAXA BepiColombo Call of Duty: il prossimo titolo del franchise con Game Pass secondo il Wall Street Journal

Call of Duty: il prossimo titolo del franchise con Game Pass secondo il Wall Street Journal