AMD Opteron Shanghai: quad core ora a 45 nanometri

In anticipo rispetto ai tempi AMD presenta la nuova generazione di processori Opteron quad core, basati su architettura nota con il nome in codice di Shanghai e costruiti con tecnologia produttiva a 45 nanometri. Frequenze incrementate, maggiori prestazioni ma consumi sotto controllo

di Paolo Corsini pubblicato il 13 Novembre 2008 nel canale Server e WorkstationAMD

Le novitŕ del core Shanghai

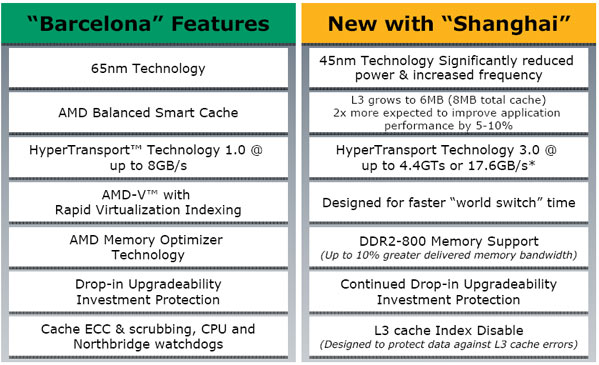

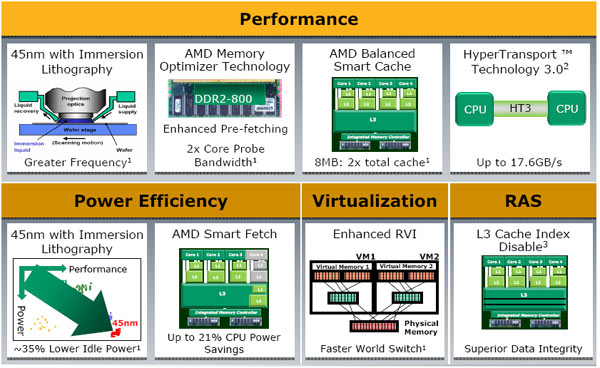

I processori AMD Opteron della famiglia Shanghai sono in primo luogo un cosiddetto die shrink: il processore č ottenuto partendo da un'architettura giŕ esistente sul mercato ed applicando a questa una tecnologia produttiva piů sofisticata, in questo caso quella a 45 nanometri. La conseguenza diretta č un contenimento delle dimensioni del die, o a paritŕ di superficie occupata la possibilitŕ di integrare un maggior numero di transistor; AMD ha optato per questa seconda strada triplicando il quantitativo di cache L3 da 2 a 6 Mbytes e inserendo varie ottimizzazioni minori all'interno del core miranti a incrementare le prestazioni velocistiche a paritŕ di clock.

L'utilizzo di una tecnologia produttiva piů sofisticata ha inoltre permesso al produttore americano di incrementare le frequenze di funzionamento a paritŕ di livelli di consumo; le cpu Opteron Shanghai, infatti, vengono proposte con le versioni standard con frequenze di clock massime al debutto pari a 2,7 GHz, mentre per i processori Opteron Barcelona il taglio di clock massimo a paritň di livello di consumo č stato pari a 2,3 GHz. Ricordiamo inoltre che a Settembre 2007, mese di presentazione ufficiale delle cpu Opteron Barcelona, AMD ha immesso sul mercato versioni con clock massimo di 2 GHz: nel giro di 1 anno il passaggio all'architettura Shanghai ha permesso di ottenere un incremento della frequenza di clock massima al debutto del 35%.

AMD ha integrato nei processori Opteron Shanghai il supporto alla tecnologia HyperTransport 3.0, grazie alla quale č possibile ottenere bandwidth massime sino a 17,6 Gbytes al secondo contro gli 8 Gbytes al secondo della soluzione Opteron Barcelona che implementa tecnologia HyperTransport 1.0. Questa nuova tecnologia potrŕ venir sfruttata pienamente solo con la prossima generazione di piattaforme Socket F per processori Opteron, attesa al debutto nel corso del 2009 in abbinamento a nuovi chipset sviluppati internamente da AMD.

La cache L3 č stata incrementata dai 2 Mbytes delle cpu Barcelona ai 6 Mbytes delle soluzioni Shanghai; č stato anche modificato in modo radicale come la cache L3 opera in particolare nel momento in cui si verificano degli errori di parity. AMD ha diviso la cache L2 in 16 distinti blocchi, che possono essere disabilitati al massimo in numero di 2 nel momento in cui si verificano errori di paritŕ; nel momento in cui i blocchi difettori dovessero essere in numero superiore a 2 il processore comunicherŕ al sistema questo malfunzionamento, che non incide sul corretto funzionamento del processore ma che per via dell'errore di correzione porta ad un aumento della latenza e ad un impatto negativo sulle prestazioni velocistiche. Questa tecnologia sarŕ disponibile solo con la prossima generazione di piattaforme server per processori Opteron attesa nel corso del 2009, quella con la quale verrŕ implementato il supporto alla tecnologia HyperTransport 3.0.

La cache L3 č stata inoltre divisa in 4 blocchi principali, 2 da 2 Gbytes di capacitŕ ciascuno e i 2 restanti da 1 Gbyte: questa caratteristica permetterŕ, non tanto con le soluzioni Opteron Quad Core quanto con le cpu desktop, di disabilitare selettivamente parte della cache L3 cosě da ottenere processori da prestazioni e fasce di prezzo differenti. AMD ha inoltre implementato varie ottimizzazioni dal lato virtualizzazione, riducendo i tempi di world switch ed ottenendo rispetto alle soluzioni Opteron Barcelona un incremento prestazionale quantificato nel 25%.

Il memory controller continua a restare del tipo DDR2 e a essere integrato nel processore; AMD ha implementato alcune ottimizzazioni nella forma sia di un incremento della massima frequenza di lavoro della memoria, portata a 800 MHz con moduli DDR2-800, sia a miglioramenti nel prefetching. L'integrazione nel memory controller di un buffer che memorizza i dati di prefetch permette di non dover svuotare la cache L3 da quei dati di prefetch che si rivelassero non correttamente previsti, e quindi non utili ai core per le elaborazioni che devono eseguire: sarŕ il buffer integrato nel memory controller a memorizzare i dati di prefetch e a venir svuotato e ricaricato di dati qualora le previsioni sulle informazioni che i core necessiteranno per le elaborazioni successive si siano rivelate errate.

Da ultimo una nota sul risparmio energetico: AMD ha implementato la tecnologia smart fetch, grazie alla quale č possibile ridurre il consumo del processore in idle forzando la cpu ad entrare nello stato halt nel momento in cui si trova in idle. Il beneficio diretto, stando a quanto dichiarato da AMD, č una riduzione dei consumi del 21% o di 15 Watt.

Possiamo riassumere le novitŕ architetturali implementate da AMD nelle cpu Opteron Shanghai evidenziando come queste siano di fatto un'evoluzione dell'architettura implementata nelle cpu Barcelona, non uno stravolgimento completo. Di fatto la sensazione č che Shanghai sia di fatto quello che Barcelona avrebbe dovuto essere, ma che per svariate considerazioni AMD non č stata capace di ottenere al debutto lo scorso anno.

La Formula E può correre su un tracciato vero? Reportage da Misano con Jaguar TCS Racing

La Formula E può correre su un tracciato vero? Reportage da Misano con Jaguar TCS Racing Lenovo LEGION e LOQ: due notebook diversi, stessa anima gaming

Lenovo LEGION e LOQ: due notebook diversi, stessa anima gaming_L.jpg) Nothing Ear e Ear (a): gli auricolari per tutti i gusti! La ''doppia'' recensione

Nothing Ear e Ear (a): gli auricolari per tutti i gusti! La ''doppia'' recensione Con Roborock S8 MaxV Ultra la pulizia di casa è ancora più precisa e automatizzata

Con Roborock S8 MaxV Ultra la pulizia di casa è ancora più precisa e automatizzata EK-Quantum Velocity2 Direct Die AMD Ryzen Edition: raffreddamento estremo per le CPU Ryzen 7000

EK-Quantum Velocity2 Direct Die AMD Ryzen Edition: raffreddamento estremo per le CPU Ryzen 7000 Le maggiori offerte sui robot aspirapolvere: tante novitŕ e sconti fino a 400 euro su modelli ECOVACS, roborock, Dreame e Narwal

Le maggiori offerte sui robot aspirapolvere: tante novitŕ e sconti fino a 400 euro su modelli ECOVACS, roborock, Dreame e Narwal Android Auto wireless: con questo adattatore Motorola MA1 (ottimo) diventa per tutti, a soli 69€!

Android Auto wireless: con questo adattatore Motorola MA1 (ottimo) diventa per tutti, a soli 69€! 2 portatili low cost sono scesi di prezzo! 239€ per un 12GB/512GB e CPU Intel, solo 464€ il 16GB/512GB con Ryzen 7 5700U!

2 portatili low cost sono scesi di prezzo! 239€ per un 12GB/512GB e CPU Intel, solo 464€ il 16GB/512GB con Ryzen 7 5700U! Nuovi sconti e coupon da 150€ per SAMSUNG Galaxy S24, S24+ e S24 Ultra, tutti i tagli e colori: ecco come acquistarli a prezzi super!

Nuovi sconti e coupon da 150€ per SAMSUNG Galaxy S24, S24+ e S24 Ultra, tutti i tagli e colori: ecco come acquistarli a prezzi super! Nuove scorte e prezzi ancora più giù! Motorola moto G84 12GB/256GB a 191€ e G54 8GB/256GB a 141€, da non credere!

Nuove scorte e prezzi ancora più giù! Motorola moto G84 12GB/256GB a 191€ e G54 8GB/256GB a 141€, da non credere! PC portatili aziendali a prezzi super: hanno tutti 24GB di RAM e processori potenti e si parte da 519€!

PC portatili aziendali a prezzi super: hanno tutti 24GB di RAM e processori potenti e si parte da 519€! HiSolution amplia i propri servizi e punta sempre più sulla cybersicurezza

HiSolution amplia i propri servizi e punta sempre più sulla cybersicurezza F1 24 introdurrà migliorie al modello di guida, una carriera rinnovata e molto altro ancora

F1 24 introdurrà migliorie al modello di guida, una carriera rinnovata e molto altro ancora Arriva Omnissa, che prenderà in carico i prodotti per "utenti finali" di VMware

Arriva Omnissa, che prenderà in carico i prodotti per "utenti finali" di VMware Turista americano torna dall'Europa e si trova una bolletta telefonica da 135 mila euro per il roaming

Turista americano torna dall'Europa e si trova una bolletta telefonica da 135 mila euro per il roaming Larian al lavoro su due nuovi giochi, creati con la stessa 'passione' di Baldur's Gate 3

Larian al lavoro su due nuovi giochi, creati con la stessa 'passione' di Baldur's Gate 3 Microsoft Office LTSC 2024 disponibile in anteprima pubblica su Windows e Mac

Microsoft Office LTSC 2024 disponibile in anteprima pubblica su Windows e Mac

_XXL.jpg)