Intel Xeon E5-2600v3: sino a 18 core, ora con memoria DDR4

L'architettura Haswell debutta anche nei sistemi server della famiglia Xeon con le CPU E5-2600v3. Nuove piattaforme abbinate a memoria DDR4 e molte versioni di processore a disposizione, con un numero di core massimo che cresce del 50% raggiiungendo il numero di 18.

di Paolo Corsini pubblicato il 09 Settembre 2014 nel canale Server e WorkstationIntel

Haswell per Xeon: uno sguardo all'architettura

Le CPU Xeon E5-2600v3 adottano architettura Haswell, che giŕ abbiamo visto utilizzata nelle piattaforme desktop abbinata ai processori Core della serie 4000 per sistemi socket 1150 LGA e piů recentemente nelle proposte Haswell-E, Core i7 5000, su schede madri socket 2011 LGA v3. Cosě come avvenuto in passato Intel adotta una nuova architettura prima in ambito desktop e mobile, spostandola in un secondo tempo anche per le proprie proposte destinate ai settori professionale ed enterprise. L'implementazione per sistemi Xeon dell'architettura Haswell introduce alcune differenze rispetto a quella adottata in sistemi desktop, principalmente legate al maggior numero di core a disposizione delle proposte server e alla necessitŕ di utilizzare due processori in sistemi dual socket.

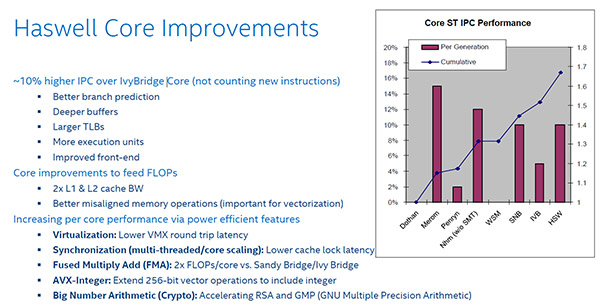

Nel confronto con l'architettura Ivy Bridge di precedente generazione Intel č stata capace di aumentare in Haswell-EP l'IPC (instruction per core) indicativamente del 10%, intervenendo ad ottimizzare alcuni degli elementi interni della CPU. Troviamo branch prediction piů efficienti, buffers e TLBs piů ampi, un maggior numero di execution units e migliorie a livello di front-end. La bandwidth delle memorie cache L1 e L2 č raddoppiata, mentre non č cambiato il rapporto tra numero di core e dimensione della cache last level (LLC) che č sempre pari a 2,5 Mbytes per ciascun core. Avendo aumentato il numero di core massimi presenti nei processori č ovviamente cresciuta di dimensione la last level cache, che raggiunge un massimo di ben 45 Mbytes.

Accanto a questo Intel ha integrato varie migliorie nella gestione della virtualizzazione, ha esteso il supporto AVX con registri a 256bit anche per i calcoli di tipo intero e ha raddoppiato le prestazioni con elaborazioni di tipo Fused Multiply Add (FMA) rispetto alle architetture di precedente generazione. L'architettura, pur trattandosi di una fase cosiddetta Tock nella sequenza di nuove CPU sviluppate da Intel, riprende quanto di valido giŕ visto in Ivy Bridge affinandone le caratteristiche e ottenendo un incremento dell'IPC che č in linea con quanto registrato in passato nelle precedenti fasi Tock nel passaggio da Westmere a Sandy Bridge, e prima ancora da Penryn a Nehalem. L'approccio scelto da Intel anche in questo caso č quindi di tipo evolutivo: con Xeon E5-2600v3 aumenta sensibilmente il numero massimo di core integrati nelle versioni di fascia piů alta rispetto alla famiglia Xeon E5-2600v2, introducendo varie ottimizzazioni che mirano a fare in modo che i singoli core possano venir sfruttati al meglio senza incontrare evidenti colli di bottiglia che andrebbero a vanificarne in parte la disponibilitŕ.

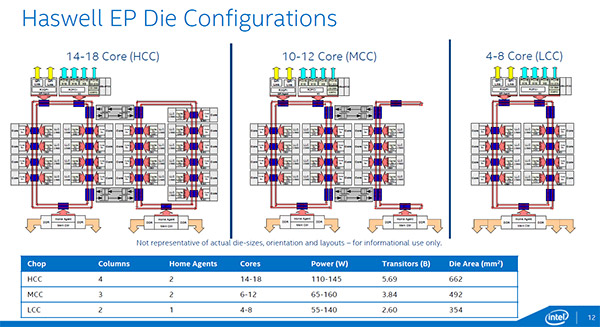

Intel ha sviluppato 3 differenti versioni di die per i processori Xeon E5-2600v3, in funzione del numero massimo di core che vengono in essi integrati. In questo modo č possibile per l'azienda ottimizzare le dimensioni del die, e quindi il costo richiesto per la sua produzione, in funzione della specifica versione di processore che viene proposta ai clienti. Vediamo in dettaglio quali siano queste 3 versioni di die e le caratteristiche abbinate:

- LCC č la versione di die adottata per le implementazioni di CPU Xeon E5-2600v3 con un numero di core variabile da 4 sino a 8, con TDP compreso tra 55 Watt e 140 Watt e un singolo home agent. Il die ha una superficie complessiva di 354 millimetri quadrati e integra circa 2,6 miliardi di transistor al proprio interno. La struttura vede un ring dual, due colonne di core e un singolo controller memoria.

- MCC č la versione di die adottata per processori con un numero di core variabile da un minimo di 6 sino a un massimo di 12, con TDP che variano da 65 Watt sino a 160 Watt. In questo caso sono presenti 2 home agent e due ring di tipo dual con 3 colonne di core x86; i memory controller ora sono due. La superficie del die raggiunge i 492 millimetri quadrati e i transistor integrati raggiungono la soglia di 3,84 miliardi.

- HCC č la versione piů complessa di die, per le versioni di CPU con un numero di core variabile da 14 a 18. Anche in questo caso troviamo 2 home agents con due ring dual e core disposti su 4 colonne, sempre con due controller memoria integrati. L'elevato numero di core presenti in quest'ultimo die ha ripercussioni dirette in termini di superficie del die (662 millimetri quadrati) e di numero di transistor (5,69 miliardi). Il TDP per le versioni di processore basate su configurazione HCC varia da 120 Watt sino a 145 Watt.

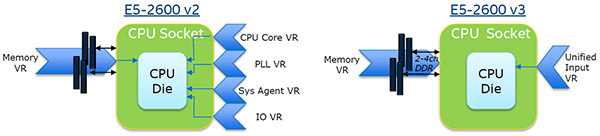

Altra novitŕ dei processori Xeon E5-2600v3 č l'integrazione nel die dei regolatori di tensione della CPU, non piů presenti quindi nella scheda madre. La necessitŕ di adottare con questi processori un nuovo socket, quindi nuove schede madri, per via dell'adozione di memoria DDR4 ha permesso ad Intel di integrare anche la circuiteria di alimentazione, un passaggio che permette di gestire in modo piů efficiente il consumo della CPU. Regolatori di tensione integrati nel processore e non piů sulla scheda madre permettono di avere una regolazione molto piů rapida in funzione di quanto richiesto dal processore, con un range di variazione che č molto piů granulare e quindi in grado di meglio ottimizzare il consumo complessivo della piattaforma durante l'uso.

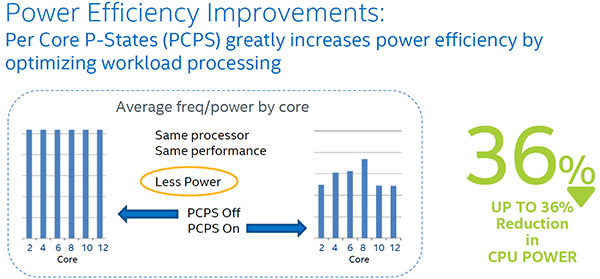

A rendere piů efficienti questi processori anche la possibilitŕ di gestire i P-state in modo specifico per ciascuno dei core, cosě da assicurare che ciascuno si trovi nella miglior condizione d'uso in termini di frequenza di clock e tensione di alimentazione in funzione della specifica elaborazione che deve essere eseguita. Ogni core puň pertanto operare indipendentemente rispetto agli altri ad una ben precisa combinazione di frequenza di clock e tensione di alimentazione.

Con Haswell Intel ha inoltre introdotto una indipendenza di clock tra ogni core e la componente Uncore. Se con Sandy Bridge e Ivy Bridge Core e Uncore potevano veder aumentare la frequenza di clock via Turbo Boost in modo parallelo, con Haswell questi componenti della CPU possono gestire in modo completamente indipendente tra di loro a seconda del tipo di carico di lavoro richiesto. Se ad esempio l'applicazione č limitata dalla potenza di calcolo dei singoli core la tecnologia Turbo Boost tenderŕ a privilegiare un incremento della frequenza di clock di questi ultimi senza necessitŕ di aumentare anche quella della componente Uncore. In modo speculare se l'applicazione č limitata dalle prestazioni del controller memoria integrato o dalla last level cache (LLC) la CPU vedrŕ aumentare la frequenza di clock della componente Uncore, lasciando se possibile invariata quella dei core cosě da evitare di incrementare il consumo oltre quanto necessario.

La Formula E può correre su un tracciato vero? Reportage da Misano con Jaguar TCS Racing

La Formula E può correre su un tracciato vero? Reportage da Misano con Jaguar TCS Racing Lenovo LEGION e LOQ: due notebook diversi, stessa anima gaming

Lenovo LEGION e LOQ: due notebook diversi, stessa anima gaming_L.jpg) Nothing Ear e Ear (a): gli auricolari per tutti i gusti! La ''doppia'' recensione

Nothing Ear e Ear (a): gli auricolari per tutti i gusti! La ''doppia'' recensione Con Roborock S8 MaxV Ultra la pulizia di casa è ancora più precisa e automatizzata

Con Roborock S8 MaxV Ultra la pulizia di casa è ancora più precisa e automatizzata EK-Quantum Velocity2 Direct Die AMD Ryzen Edition: raffreddamento estremo per le CPU Ryzen 7000

EK-Quantum Velocity2 Direct Die AMD Ryzen Edition: raffreddamento estremo per le CPU Ryzen 7000 Le maggiori offerte sui robot aspirapolvere: tante novitŕ e sconti fino a 400 euro su modelli ECOVACS, roborock, Dreame e Narwal

Le maggiori offerte sui robot aspirapolvere: tante novitŕ e sconti fino a 400 euro su modelli ECOVACS, roborock, Dreame e Narwal Android Auto wireless: con questo adattatore Motorola MA1 (ottimo) diventa per tutti, a soli 69€!

Android Auto wireless: con questo adattatore Motorola MA1 (ottimo) diventa per tutti, a soli 69€! 2 portatili low cost sono scesi di prezzo! 239€ per un 12GB/512GB e CPU Intel, solo 464€ il 16GB/512GB con Ryzen 7 5700U!

2 portatili low cost sono scesi di prezzo! 239€ per un 12GB/512GB e CPU Intel, solo 464€ il 16GB/512GB con Ryzen 7 5700U! Nuovi sconti e coupon da 150€ per SAMSUNG Galaxy S24, S24+ e S24 Ultra, tutti i tagli e colori: ecco come acquistarli a prezzi super!

Nuovi sconti e coupon da 150€ per SAMSUNG Galaxy S24, S24+ e S24 Ultra, tutti i tagli e colori: ecco come acquistarli a prezzi super! Nuove scorte e prezzi ancora più giù! Motorola moto G84 12GB/256GB a 191€ e G54 8GB/256GB a 141€, da non credere!

Nuove scorte e prezzi ancora più giù! Motorola moto G84 12GB/256GB a 191€ e G54 8GB/256GB a 141€, da non credere! PC portatili aziendali a prezzi super: hanno tutti 24GB di RAM e processori potenti e si parte da 519€!

PC portatili aziendali a prezzi super: hanno tutti 24GB di RAM e processori potenti e si parte da 519€! HiSolution amplia i propri servizi e punta sempre più sulla cybersicurezza

HiSolution amplia i propri servizi e punta sempre più sulla cybersicurezza F1 24 introdurrà migliorie al modello di guida, una carriera rinnovata e molto altro ancora

F1 24 introdurrà migliorie al modello di guida, una carriera rinnovata e molto altro ancora Arriva Omnissa, che prenderà in carico i prodotti per "utenti finali" di VMware

Arriva Omnissa, che prenderà in carico i prodotti per "utenti finali" di VMware Turista americano torna dall'Europa e si trova una bolletta telefonica da 135 mila euro per il roaming

Turista americano torna dall'Europa e si trova una bolletta telefonica da 135 mila euro per il roaming Larian al lavoro su due nuovi giochi, creati con la stessa 'passione' di Baldur's Gate 3

Larian al lavoro su due nuovi giochi, creati con la stessa 'passione' di Baldur's Gate 3 Microsoft Office LTSC 2024 disponibile in anteprima pubblica su Windows e Mac

Microsoft Office LTSC 2024 disponibile in anteprima pubblica su Windows e Mac

_XXL.jpg)