Un server rack ad alta efficienza con processori Tilera e 512 core

Tilera, in collaborazione con Quanta, presenta una soluzione server a 2 unit‡ rack che integra 4 sistemi dual socket indipendenti per un totale di 512 core. Ottima efficienza, ma solo con applicazioni che ne sfruttino al meglio l'architettura

di Paolo Corsini pubblicata il 24 Giugno 2010, alle 14:30 nel canale Private CloudUn sistema server da 2 unit‡ rack d'ingombro, al cui interno trovano posto un totale di 512 core. E' questo il risultato al quale Ë giunta Tilera Corp., azienda specializzata nello sviluppo di architetture multicore che trovano ideale ambito di utilizzo in quelle applicazioni che possono venir scalate al meglio su tanti core di semplice architettura e ridotta potenza elaborativa, beneficiando di livelli di consumo estremamente contenuti. Tilera ha fornito la base architetturale e i processori, mentre la produzione materiale del sistema server, chiamato S2Q, Ë stata svolta da Quanta Computer Inc.

Il processore Tilera TilePro64, alla base di questo sistema, utilizza una particolare architettura che permette di ottenere valide prestazioni velocistiche non con qualsiasi tipo di applicazione ma con quelle che ad essa ben si adattano. I "tile", termine con il quale Ë indicato ciascun core, sono interconnessi tra loro grazie al network iMesh di Tilera. Ogni core Ë caratterizzata dalla presenza di pipeline a 3 stadi in grado di gestire fino a tre istruzioni per ciclo di clock. Ciascun core Ë provvisto di 32KB di cache L1 per istruzioni e di una identica quantit‡ di cache L1 per i dati e di 256KB di cache di secondo livello. Ogni tile puÚ operare in maniera indipendente oppure in collaborazione con altri tile, a seconda delle esigenze della specifica applicazione in uso.

I processori della famiglia Tile-Gx integrano controller memoria e controller di input-output eliminando cosÏ la necessit‡ di un northbridge esterno o di un southbridge. La tecnologia TileDirect Technology puÚ gestire gli I/O direttamente nelle cache del tile per offrire prestazioni a bassa latenza. I processori TILE-Gx possono essere programmati in C e C++, dando modo agli sviluppatori di appoggiarsi sugli investimenti software esistenti. I "tile" possono inoltre essere raggruppati in cluster al fine di mettere a disposizione per ciascuna applicazione il necessario quantitativo di potenza computazionale.

Stando a quanto affermato dal produttore, una soluzione server che utilizza 8 processori Tilera TilePro64, ciascuno dotato di 64 core per un totale di 512, vanta un consumo contenuto in 400 Watt di picco. 12 server di questo tipo, installati in mezzo armadio rack, richiedono 5 KW per veir alimentati e forniscono le prestazioni equivalenti a 100 server basati su processori Intel Xeon dual socket, configurazione che richiede un consumo di 25 KW.

Il server SQ2, soluzione che prossimamente verr‡ resa disponibile sul mercato, integra 4 schede madri dual socket per un totale di 512 core; per ogni scheda madre sono presenti 16 slot memoria, 4 schede di rete Gigabit, 4 schede di rete 10 Gigabit e 4 porte per la gestione da console del server. Per ogni server sono abbinati un massimo di 6 hard disk da 2 pollici e 1/2, accessibili dal pannello frontale.

Quali sono gli ambiti di utilizzo di riferimento di questa soluzione? Tutte quelle applicazioni che per loro natura possono beneficiare delle particolarit‡ architettuali delle soluzioni Tilera. Questi processori sembrano dare ottimi livelli di scalabilit‡ in ambiente LAMP (Linux, Apache, MySQL e PHP), sfruttando una distribuzione custom della quale non sono stati ancora forniti dettagli precisi. Un'azienda interessata alla elevata potenza di elaborazione di queste soluzioni, abbinata a consumi ridotti, deve quindi prima attentamente verificare che le applicazioni che verranno utilizzate siano in grado di ben operare con questa architettura, oppure se non sia preferibile l'utilizzo di tradizionali server x86.

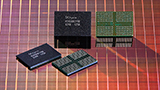

La roadmap Tilera Ë particolarmente aggressiva. Per il 2011 si prevede il debutto dei nuovi core Tile-Gx, con un incremento del loro numero da 64 sino a 100 per ogni socket grazie ad uno shrink dalla tecnologia a 90 nanometri fino a quella a 40 nanometri. In seguito, per il 2013, Ë previsto il lancio di una nuova generazione di core a 28 nanometri indicati con il nome in codice di Stratton che permetter‡, secondo i piani dell'azienda, di superare i 200 core per socket.

Ulteriori informazioni sono disponibili sul sito Tilera a questo indirizzo.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è líottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  La sonda spaziale NASA Psyche comunica via laser con la Terra da 226 milioni di chilometri

La sonda spaziale NASA Psyche comunica via laser con la Terra da 226 milioni di chilometri Dacia Duster, prima guida: con le versioni ibride spacca il mercato

Dacia Duster, prima guida: con le versioni ibride spacca il mercato Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà

Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti

RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti Amazon scatenata: iPad a 399Ä, airfryer 38Ä, smartphone, portatili e moltissimi articoli in svendita!

Amazon scatenata: iPad a 399Ä, airfryer 38Ä, smartphone, portatili e moltissimi articoli in svendita! SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM

SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM Oggi 459Ä per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD!

Oggi 459Ä per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD! Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

Wacom Movink: per la prima volta il display interattivo ha uno schermo OLED

6 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - infoL'unione fa la forza!!

ArsTecnica parla di:

Tilera's cores implement a very simple VLIW design with two integer ALUs and a load-store pipe (at least, I'm pretty sure that the third execution pipeline is load-store).

Quindi magari sono 3 stage di esecuzione, più che 3 stage di lunghezza. Quindi permetterebbe di eseguire 3 istruzioni contemporaneamente.

La ISA di queste CPU è di tipo VLIW, quindi con parallelismo esplicito nell'opcode. Con 3 sole pipeline è sicuramente più semplice che in Itanium...

Senza contare che non sono CPU general purpose, mancano infatti di FPU.

si parla di "3-way VLIW". Pero' per il TILE-Gx invece si parla di 3 stadi di pipeline... mah!

Cmq, se vi interessa, qui:

http://www.stanford.edu/class/ee380...e-20092010.html

c'e' un intervento del fondatore di Tilera (ovviamente professore del MIT

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".