Quasi pronte le specifiche PCI Express 4.0, mentre quelle 5.0 si affacciano all'orizzonte

PCI-SIG č pronta a finalizzare le specifiche PCI Express 4.0, che guideranno le caratteristiche tecniche dei componenti di prossima generazione con un raddoppio della bandwidth massima

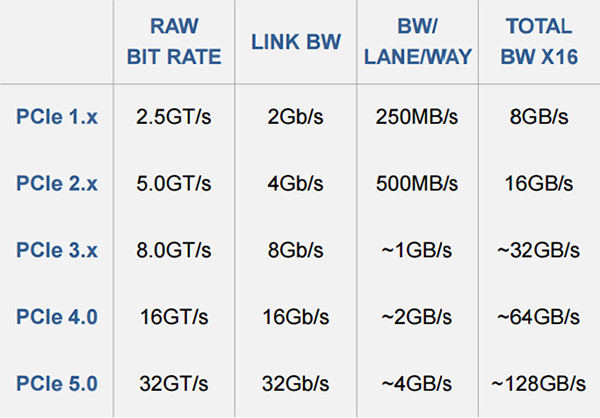

di Paolo Corsini pubblicata il 09 Giugno 2017, alle 11:01 nel canale Scienza e tecnologiaPCI-SIG, l'organismo che ratifica le specifiche legate al funzionamento e alla compatibilità delle periferiche PCI Express, ha annunciato le nuove specifiche PCI Express 4.0 alle aziende che sono affiliate. Al pari di quanto avvenuto in passato il nuovo sistema di interconnessione porterà ad un raddoppio della bandwidth a parità di numero di linee PCI Express utilizzate.

La disponibilità di specifiche aggiornate, con un incremento della bandwidth massima, si rivela essere particolarmente interessante non solo pensando alle esigenze delle schede video di prossima generazione ma anche per l'utilizzo in ambiti professionali come quello del mondo server. In generale le connessioni PCI Express hanno trovato utilizzo diffuso in ambito consumer quando sfruttate per le periferiche di storage più veloci, così da andare oltre alle limitazioni dell'interfaccia SATA e servirsi al meglio dell'elevata bandwidth offerta dagli SSD più recenti.

Le nuove specifiche prevedono anche la possibilità di gestire interconnessioni con un maggior numero di linee e velocità differenti, così da meglio andare incontro alle necessità di applicazioni nelle quali si richieda un consumo particolarmente contenuto. PCI-SIG ha confermato di aver già eseguito vari test con alcuni membri del consorzio per ottenere la velocità di trasferimento di 16 GT/s per interconnessione così come previsto dalle specifiche. Le specifiche PCIe 4.0 sono alla revision 0.9: i membri del PCI-SIG hanno tempo sino al prossimo 9 agosto per sottoporre osservazioni e note a riguardo.

Per il 2019 si attende il debutto delle specifiche PCI Express 5.0, che permetteranno di ottenere un ulteriore raddoppio della bandwidth massima complessiva rispetto a quello delle specifiche PCI Express 4.0. Con una connessione 16x full duplex le specifiche PCIe 5.0 permettono di ottenere sulla carta una bandwidth di trasferimento massima teorica di ben 128 GB/s, un dato doppio rispetto ai 64 GB/s delle specifiche PCIe 4.0 e quadruplo prendendo quale riferimento l'attuale implementazione PCIe 3.0.

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone'

Recensione Zenfone 11 Ultra: il flagship ASUS ritorna a essere un 'padellone' Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA

Appian: non solo low code. La missione è l’ottimizzazione dei processi con l'IA Lenovo ThinkVision 3D 27, la steroscopia senza occhialini

Lenovo ThinkVision 3D 27, la steroscopia senza occhialini  La Cina ha lanciato la missione Shenzhou-18 con tre astronauti diretti verso la stazione spaziale cinese

La Cina ha lanciato la missione Shenzhou-18 con tre astronauti diretti verso la stazione spaziale cinese La sonda spaziale NASA Psyche comunica via laser con la Terra da 226 milioni di chilometri

La sonda spaziale NASA Psyche comunica via laser con la Terra da 226 milioni di chilometri Dacia Duster, prima guida: con le versioni ibride spacca il mercato

Dacia Duster, prima guida: con le versioni ibride spacca il mercato Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà

Arriva l'ok da Parlamento europeo sul diritto alla riparazione. Ecco cosa cambierà RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti

RISC-V: l'uso dell'ISA open-source da parte della Cina preoccupa gli Stati Uniti Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita!

Amazon scatenata: iPad a 399€, airfryer 38€, smartphone, portatili e moltissimi articoli in svendita! SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM

SK hynix, costruzione della Fab M15X ai nastri di partenza: previsto boom delle memorie HBM Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD!

Oggi 459€ per utenti Prime il portatile low cost con AMD Ryzen 7 5700U (8C/16T a 4,3GHz), 16GB RAM, SSD 512GB, Full HD! Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online

Sta per succedere! La prima gara a guida autonoma sarà il 27 aprile: come vederla online Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli

Parthenope: un nuovo RPG investigativo tutto italiano e ambientato a Napoli Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare

Urbanista Malibu: ecco come va la cassa Bluetooth con ricarica solare Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam

Gas Station Simulator è costato 110 mila euro e ha guadagnato più di 10 milioni su Steam AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

AOC Graphic Pro U3, tre nuovi monitor per i professionisti creativi

9 Commenti

Gli autori dei commenti, e non la redazione, sono responsabili dei contenuti da loro inseriti - info4 x 16 fa 64 non 128 come nell'ultima riga e allo stesso modo su..

4 x 16 fa 64 non 128 come nell'ultima riga e allo stesso modo su..

ma il pci 4.0 è la penultima riga

Non c'entra nulla, l'ultima colonna ha valori doppi rispetto al dovuto( moltiplicare per 16 il valore di una singola linea).

giustissimo

La penultima colonna indica la banda per linea per via (lettura o scrittura).

250MB/s * 16 lanes * 2 ways (Lettura e Scrittura) = 8GB\s (PCIe 1.x)

250MB/s * 16 lanes * 2 ways (Lettura e Scrittura) = 8GB\s (PCIe 1.x)

ma infatti secondo me Emin001 nn ha ben capito la tabella, e meno ancora "tuttodigitale" che gli da ragione

1) Ti ho solo fatto notare che il dubbio di Rubberick non era legato al PCIe 4.0. Se io non ho capito nulla tu non hai nemmeno lontanamente afferrato quanto scritto da Rubberick.

2) Quella tabella gira da anni con la dicitura per esteso "Bandwidth per lane direction"(es. http://www.anandtech.com/show/2412/2) e non abbreviato BW/LANE/WAY quindi stai tranquillo che ho ben capito(vale anche per konamikcej) ma non sono affatto d'accordo. I valori dell'ultima colonna vanno dimezzati per coerenza con i valori scritti in precedenza o quanto meno va scritto che si tratta di un valore globale e non sono il solo a pensarla in questo modo visto che non è difficile trovare tabelle e/o scritti con i valori non aggregati:

http://www.ibmsystemsmag.com/getatt...a-ddceb52d43f5/ https://image.slidesharecdn.com/pci...g?cb=1408809368 http://hexus.net/tech/news/mainboar...power-delivery/ http://www.hardwaresecrets.com/ever...-pci-express/3/.

Devi effettuare il login per poter commentare

Se non sei ancora registrato, puoi farlo attraverso questo form.

Se sei già registrato e loggato nel sito, puoi inserire il tuo commento.

Si tenga presente quanto letto nel regolamento, nel rispetto del "quieto vivere".